FDCAN探路

CAN with flexible data-ratev

1.参考资料

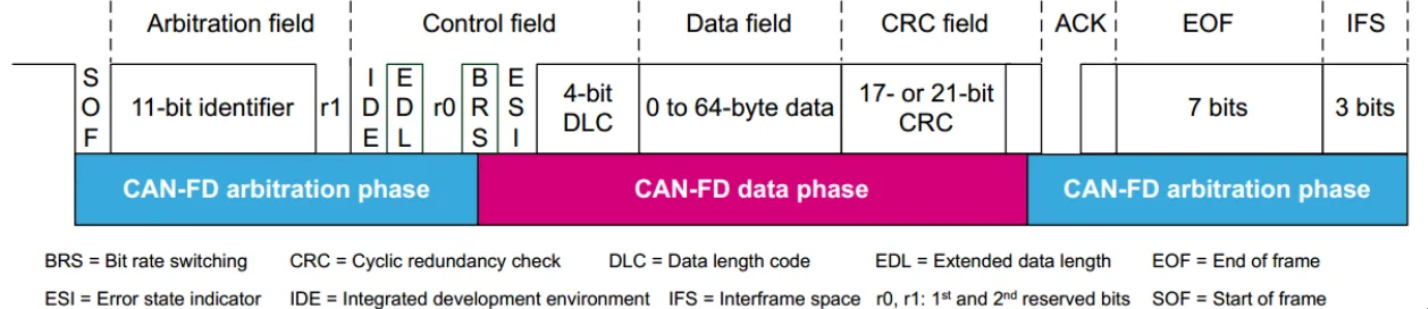

2.FDCAN数据格式

第一个仲裁阶段(The first arbitration phase)是一条消息,其中包含:

- 帧开始(SOF)。

- ID 号和其他位,指示消息的目的(提供或请求数据),以及速度和格式配置(CAN 或 CAN-FD)。

数据传输阶段(The data transmission phase)包括:

(1)数据长度代码(DLC),指示消息包含多少数据字节。

(2)用户希望发送的数据。

(3)检查循环冗余序列(CRC)。

(4)显性位。

第二个仲裁阶段(The second arbitration phase)包含:

(1)总线上其他节点发送的确认(ACK)的接收器(如果至少有一个接收器成功收到消息)

(2)帧尾(EOF),在 IFS 期间不传输任何消息:目标是将当前帧与下一帧分开。

3.FDCAN通信协议

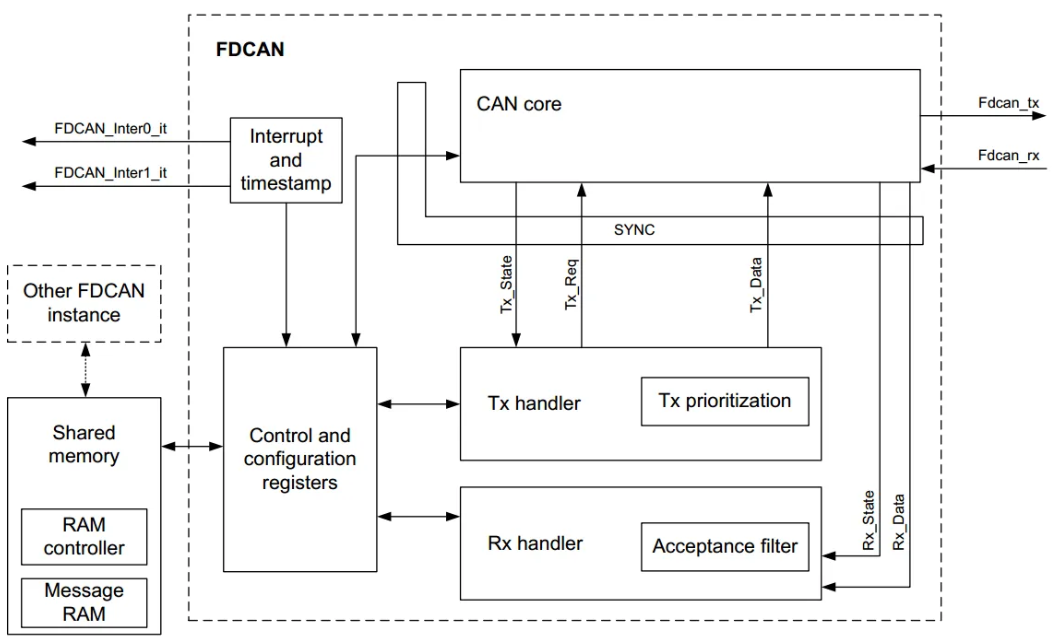

3.1 整体框架

通过这个框图要了解到以下信息:

(1) CANFD1 和 CANFD2 共用一个 RAM 空间。

(2)每个 CANFD 都有自己的内核。

(3) CAN 内核实现协议控制和收发移位寄存器。

(4) Tx handler 控制消息从 CAN 消息 RAM 到 CAN 内核。

(5) Rx handler 控制 CAN 内核到 CAN 消息 RAM。

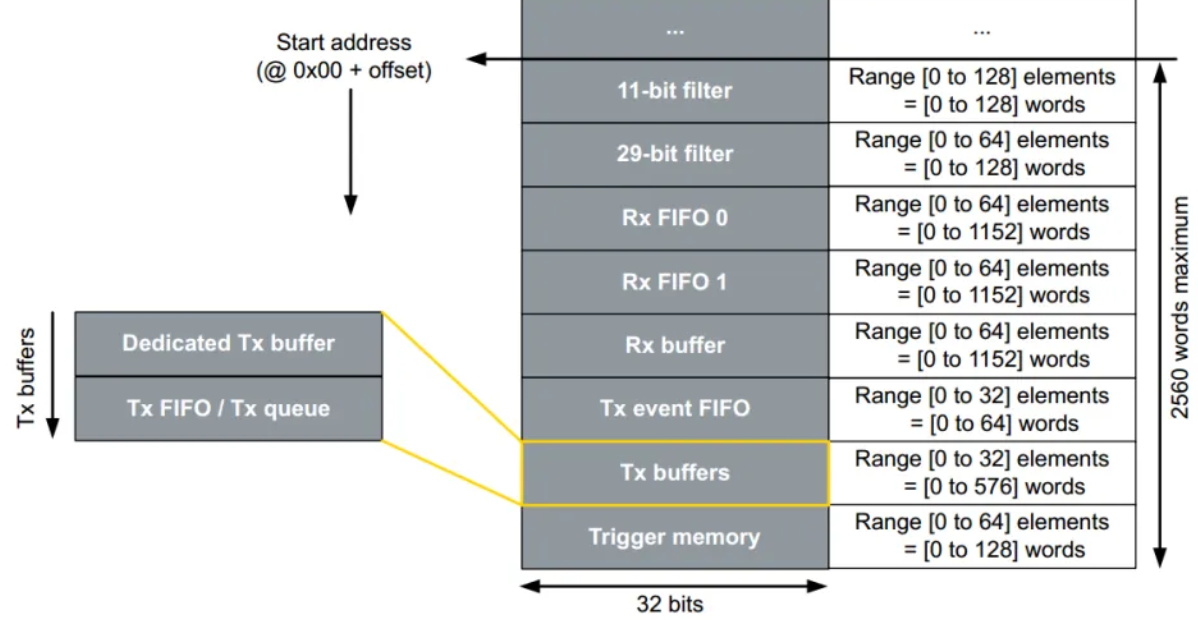

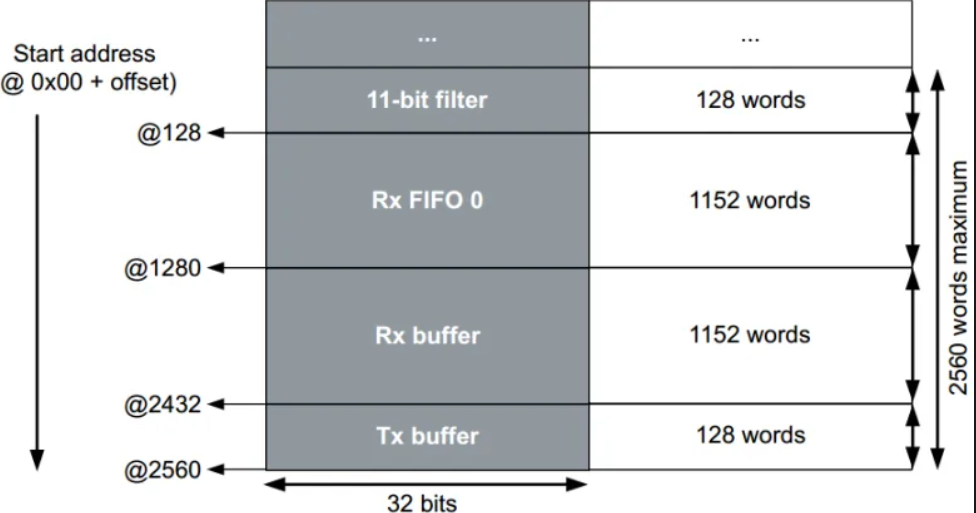

3.2 RAM空间

CAN-FD 上有效负载的增加可以更有效的将内存都利用起来,并允许更多消息要存储在分配的存储空间中。总的专用 RAM 大小是 2560 个32bit 数据。

FDCAN 外设的所有部分都可以由用户配置。 所有部分的所有元素之和必须不能超过 CAN 消息 RAM的总大小。 该 RAM 通过以下方式提高了灵活性和性能:从而有可能消除未使用的部分,并为其他部分扩展足够的内存。在 CAN 消息中以动态且连续的方式分配每个部分(按照上图顺序); 但是为了避免超出RAM 的风险并且出于可靠性的原因,没有将特定的开始和结束地址分配给每个部分。

例子:

在此示例中, RAM 中的分配按以下顺序进行:

(1)在 ID-11 位部分分配 128 个字。

(2)保留 1152 个字用于接收 Rx FIFO 0 部分中的元素。

(3)保留 1152 个字,用于接收 Rx 缓冲区中的元素。

(4)为发送缓冲区中发送的元素保留 128 个字。

3.3 过滤器

过滤器是用于接收的,发送的时候无需设置过滤器,这点一定要整明白

4. FDCAN收发机制

可以配置三种传输机制:

Tx buffer , Tx queue 和 Tx FIFO 并可以通过Rx buffer 和 Rx FIFO 接收

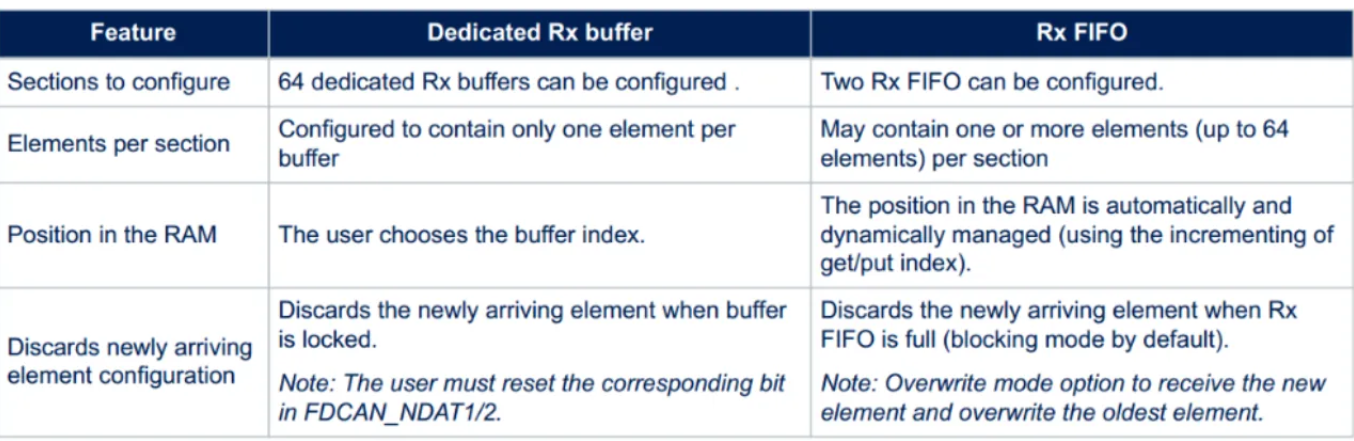

4.1 FDCAN接收机制

RX buffer模式适用于不可覆盖的重要信号,按照指定好的buffer去收取,适合实时性要求高的关键数据。

RX FIFO 模式可配置为新报文覆盖最旧报文的覆盖模式,自动管理内存, 适合处理高频率、低优先级的连续数据流(如传感器数据)。

电机控制场景下一般选FIFO就可

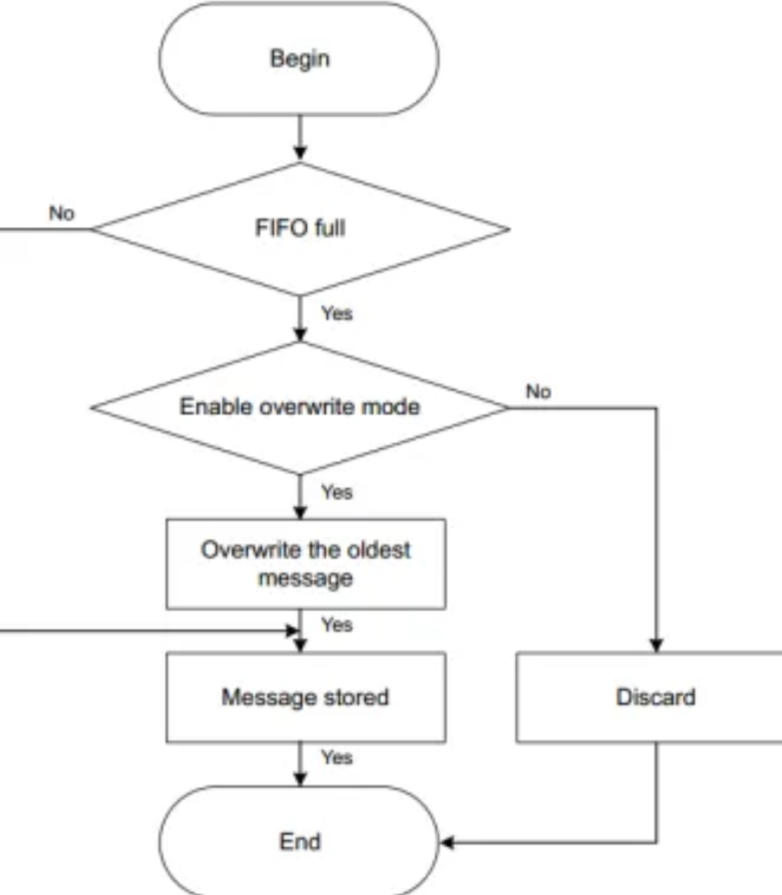

FIFO接收

可以在 CAN 消息 RAM 中配置两个 Rx FIFO。 每个 Rx FIFO 部分最多可存储 64 个元素。每个元素存储在一个 Rx FIFO 元素中。可以通过 FDCAN_RXESC 寄存器分别为每个 Rx FIFO 配置 Rx FIFO 元素的大小。 Rx FIFO 元素大小定义了可以存储一个接收元素的数据字段字节数。 一个大小 Rx FIFO 元素由前面 RAM 管理中指定的公式定义。

(1)阻塞模式:这是 Rx FIFO 的默认操作模式,没有其他元素写入 RxFIFO,直到至少一个元素已被读出。

(2)覆盖模式: Rx FIFO 中接受的新元素将覆盖 Rx FIFO 中最旧(最先接收的数据)的元素并且 FIFO 的put 和 get 索引加 1。

要从 Rx FIFO 读取元素, CPU 必须执行以下步骤:

(1)读取寄存器 FDCAN_RXF1S 以了解 Rx FIFO 的状态。

(2)按照以下公式计算 RAM 中最旧的元素的地址:

Oldest element address = CAN_message_RAM_base_address + FDCAN_RXF1C.F1SA (start address) + FDCAN_RXF1S.F1GI (get Index) x Rx FIFO_element_size.

(3)从计算出的地址中读取元素

1 | void HAL_FDCAN_RxFifo0Callback(FDCAN_HandleTypeDef *hfdcan, uint32_t RxFifo0ITs) |

RX BUFFER接收

FDCAN 支持多达 64 个专用 Rx buffers。 每个专用的 Rx buffers 可以存储一个元素。专用 Rx buffers的大小可以通过 FDCAN_RXESC 寄存器进行配置。 Rx buffers 大小定义可以存储多少个接收元素的数据字段字节。 专用 Rx buffers 的大小由前面 RAM 组织中描述的公式定义

要从专用 Rx 缓冲区读取元素, CPU 必须执行以下步骤:

(1)检查 FDCAN_NDAT1 / 2 中的位,以了解是否有新元素到达专用 Rx 缓冲区。

(2)计算 CAN 消息 RAM 中元素的地址,如以下公式所示:

Reference Rx buffer address = CAN_message_RAM_base_address + FDCAN_RXBC.RBSA (startaddress) + dedicated Rx buffer index x Rx_Buffer_element_size.

(3)从计算出的地址中读取消息。

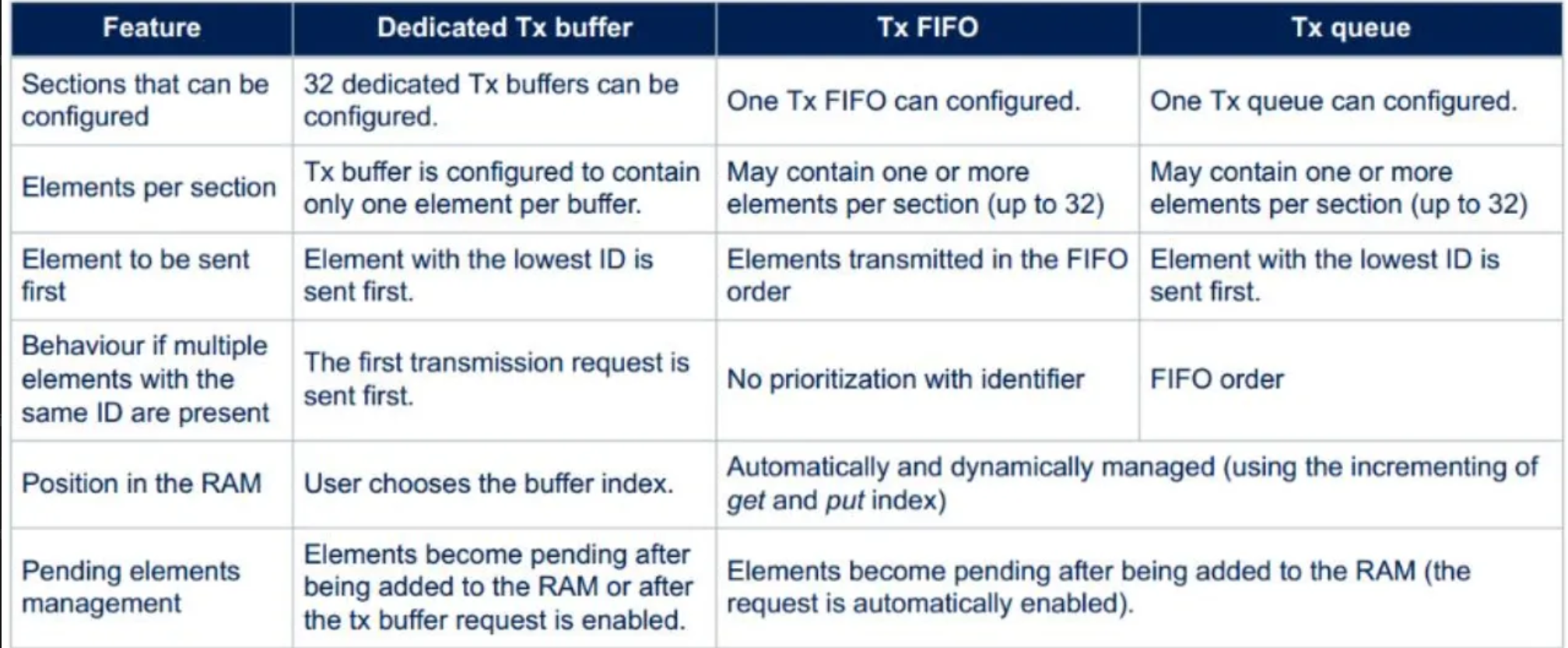

4.2 FDCAN发送机制

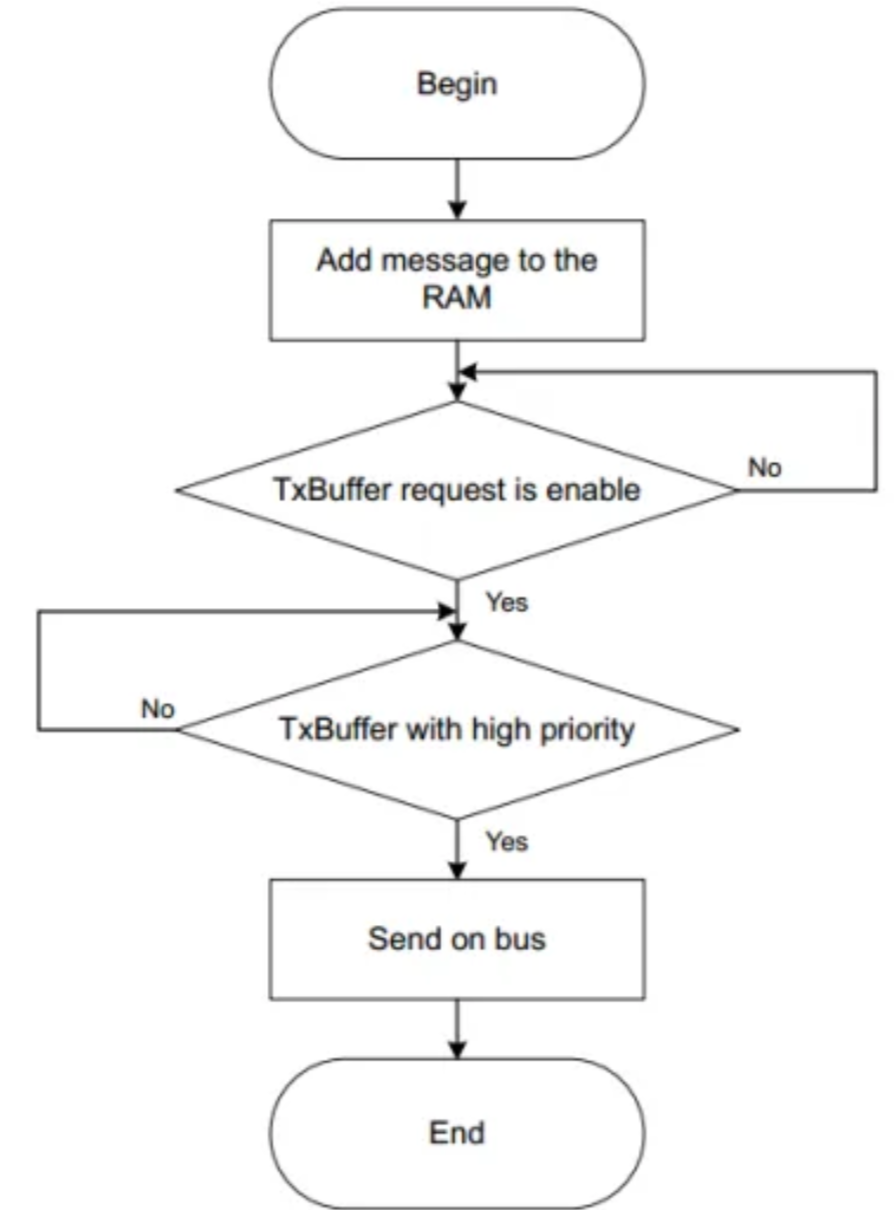

Dedicated Tx buffers

专用 Tx buffer 的数量是通过 FDCAN_TXBC 寄存器中的 NTDB [5: 0]字段配置的。每个专用 Tx buffer配置有特定的标识符,以仅存储一个元素。

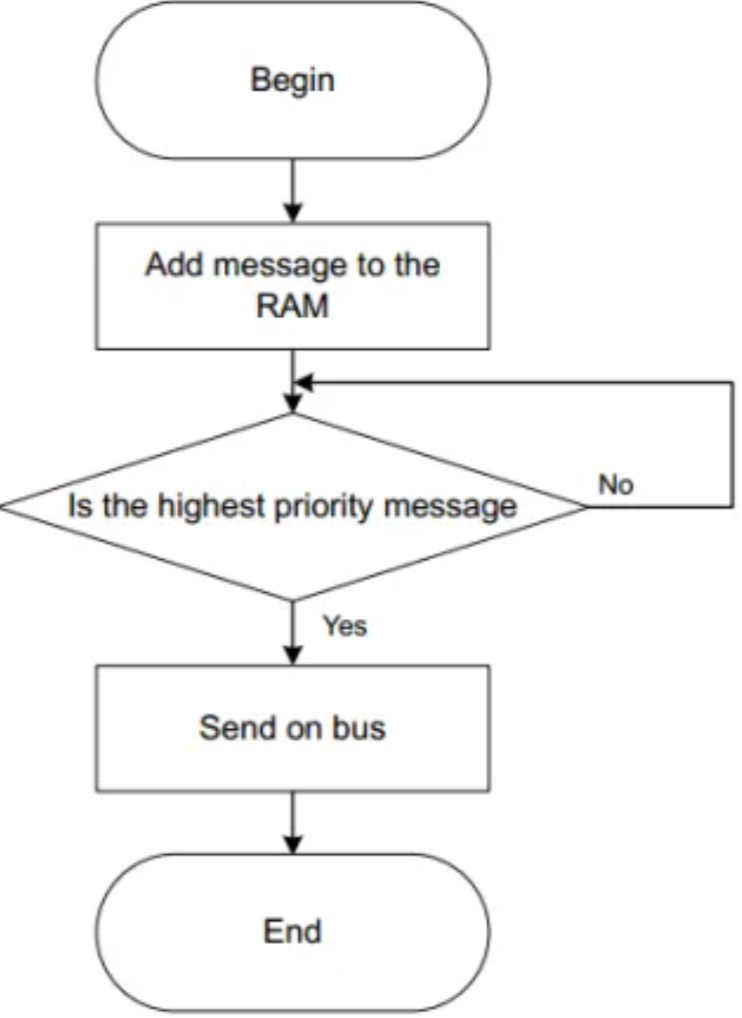

根据最低标识符(最高优先级)发送

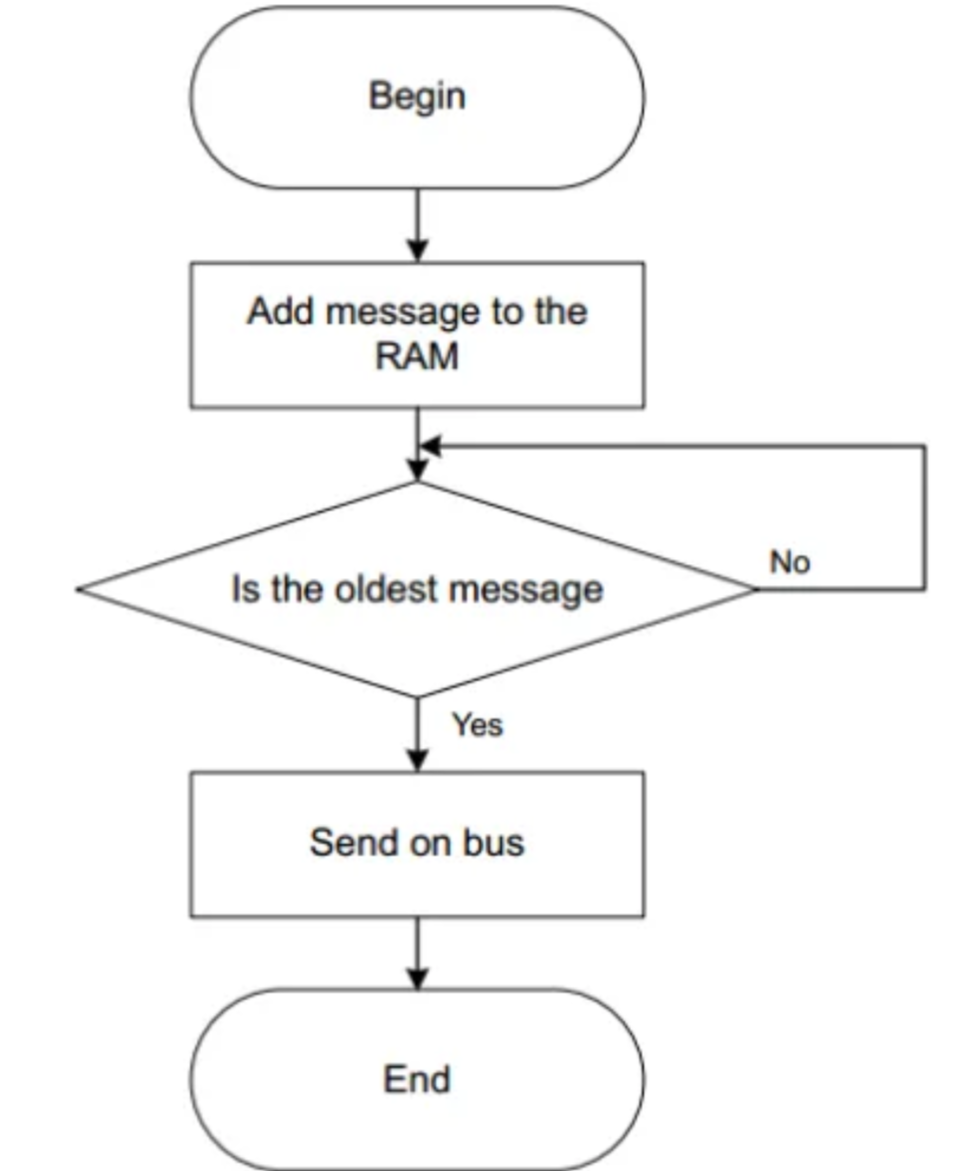

Tx FIFO

传输与各个标识符的优先级无关,因为 FIFO 首先发送出去。

Tx queue

通过将 1 写入 FDCAN_TXBC 中的 TFQM 位来配置 Tx 队列操作。 Tx 中存储的元素从具有最低标识符(最高优先级)的 Tx 队列缓冲区开始传输队列。与专用 Tx 缓冲区相比, RAM 上的位置是自动动态管理的,因此消息标识符不固定为预定义的 Tx 缓冲区索引。

- 标题: FDCAN探路

- 作者: Porcovsky

- 创建于 : 2025-06-15 21:51:45

- 更新于 : 2025-06-15 22:00:34

- 链接: https://pocro.github.io/2025/06/15/FDCAN探路/

- 版权声明: 本文章采用 CC BY-NC-SA 4.0 进行许可。